This documentation is released under the Creative Commons license

This documentation is released under the Creative Commons licensePrototype for modules providing Ethernet switch functionality. These modules handle the mapping between ports and MAC addresses, and forward frames (EtherFrame) to appropriate ports.

Functions:

Address caching is modeled by a fixed-size lookup table. When the table is full, the oldest address is kicked out of the cache.

Entries are also deleted if their age exceeds a certain limit.

If needed, address tables can be pre-loaded from text files at the beginning of the simulation; this controlled by the addressTableFile module parameter.

This module is not a concrete implementation, it just defines gates and parameters a IMACRelayUnit should have. Concrete inplementations add capacity and performance aspects to the model (number of frames processed per second, amount of memory available in the switch, etc.) C++ implementations can subclass from the class MACRelayUnitBase.

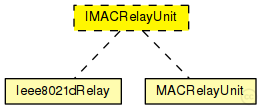

Known implementations are MACRelayUnit and Ieee8021dRelay.

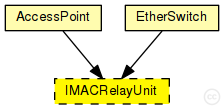

The following diagram shows usage relationships between types. Unresolved types are missing from the diagram.

The following diagram shows inheritance relationships for this type. Unresolved types are missing from the diagram.

| Name | Type | Description |

|---|---|---|

| AccessPoint | compound module |

A generic access point supporting multiple wireless radios, and multiple ethernet ports. The type of the ethernet MAC, relay unit and wireless card can be specified as parameters. |

| EtherSwitch | compound module |

Model of an Ethernet switch. |

| Name | Value | Description |

|---|---|---|

| display | i=block/switch |

// // Prototype for modules providing Ethernet switch functionality. // These modules handle the mapping between ports and MAC addresses, // and forward frames (~EtherFrame) to appropriate ports. // // Functions: // - relays frames based on their dest MAC addresses (dest-->port mapping) // - models finite buffer size (drops) and finite processing power (latency, queueing) // // Address caching is modeled by a fixed-size lookup table. // When the table is full, the oldest address is kicked out of the cache. // // Entries are also deleted if their age exceeds a certain limit. // // If needed, address tables can be pre-loaded from text files at the beginning // of the simulation; this controlled by the addressTableFile module parameter. // // This module is not a concrete implementation, it just defines gates and // parameters a ~IMACRelayUnit should have. Concrete inplementations add // capacity and performance aspects to the model (number of frames processed // per second, amount of memory available in the switch, etc.) // C++ implementations can subclass from the class <tt>MACRelayUnitBase</tt>. // // Known implementations are ~MACRelayUnit and ~Ieee8021dRelay. // moduleinterface IMACRelayUnit { parameters: @display("i=block/switch"); gates: input ifIn[] @labels(EtherFrame); output ifOut[] @labels(EtherFrame); input stpIn @loose; output stpOut @loose; }