This documentation is released under the Creative Commons license

This documentation is released under the Creative Commons licenseThis module implements a strict priority scheduler.

Packets arrived at the 0th gate are served first, then the packets arrived at the 1st gates, and so on.

The module implements the IPassiveQueue C++ interface.

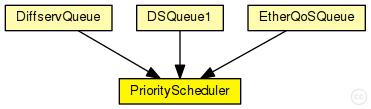

The following diagram shows usage relationships between types. Unresolved types are missing from the diagram.

The following diagram shows inheritance relationships for this type. Unresolved types are missing from the diagram.

| Name | Type | Description |

|---|---|---|

| DiffservQueue | compound module |

This is an example queue, that can be used in interfaces of DS core and edge nodes to support the AFxy (RFC 2597) and EF (RFC 3246) PHBs. |

| DSQueue1 | compound module |

Diffserv Queue used in Experiment 1.1 - 1.6 and 5.1. |

| EtherQoSQueue | compound module |

Queue module that gives the PAUSE frames a higher priority, and can be parametrized with an IOutputQueue for serving the other frames. |

| Name | Value | Description |

|---|---|---|

| display | i=block/server |

| Name | Direction | Size | Description |

|---|---|---|---|

| in [ ] | input | ||

| out | output |

// // This module implements a strict priority scheduler. // // Packets arrived at the 0th gate are served first, // then the packets arrived at the 1st gates, and so on. // // The module implements the IPassiveQueue C++ interface. // simple PriorityScheduler { @display("i=block/server"); gates: input in[]; output out; }